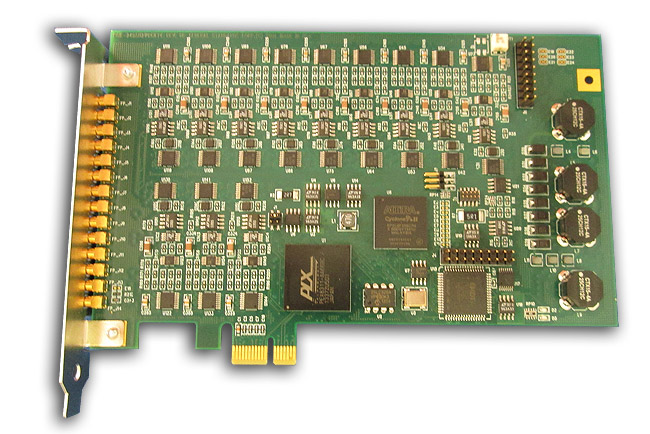

The 12-channel PCIe-24DSI12WRCIEPE analog input module provides high-density 24-bit IEPE analog input resources on a standard PCI Express module. Optimized for flexibility and performance, the board is ideal for a wide variety of applications, ranging from IEPE transducer inputs and precision voltage measurements, to the analysis of complex acoustic signals and waveforms.

Each of twelve analog input channels contains a lowpass image filter, and a delta-sigma A/D converter that provides inherent antialias suppression and sharp cutoff lowpass filtering. The inputs can be software-configured as either AC-coupled IEPE inputs with excitation current applied, or as high-impedance DC-coupled inputs with or without excitation current. An internal voltage reference can be applied through all channels to support selftest operations and autocalibration. Gain and offset trimming is performed by applying correction values that are determined during on-demand autocalibration. A linear-phase digital antialiasing filter rejects out-of-band signals, and a lowpass analog filter reject those interference signals that fall within the harmonic images of the digital filter. ADC clocking is obtained either from an external hardware source, or internally from an internal sample-rate generator. The internal generator is adjustable over a 2:1 frequency range, and is divided down within the local controller to provide individual channel sample rates from 0.4 KSPS to 105 KSPS in the high-speed clocking mode, or from 0.2 KSPS to 52 KSPS in high-resolution and low-power modes. Conversion data from all active channels is transferred to the PCI Express bus through a 256 K-sample data buffer that is supported by two DMA channels. Multiple boards can be synchronized to perform simultaneous sampling with external sync and clock connections.