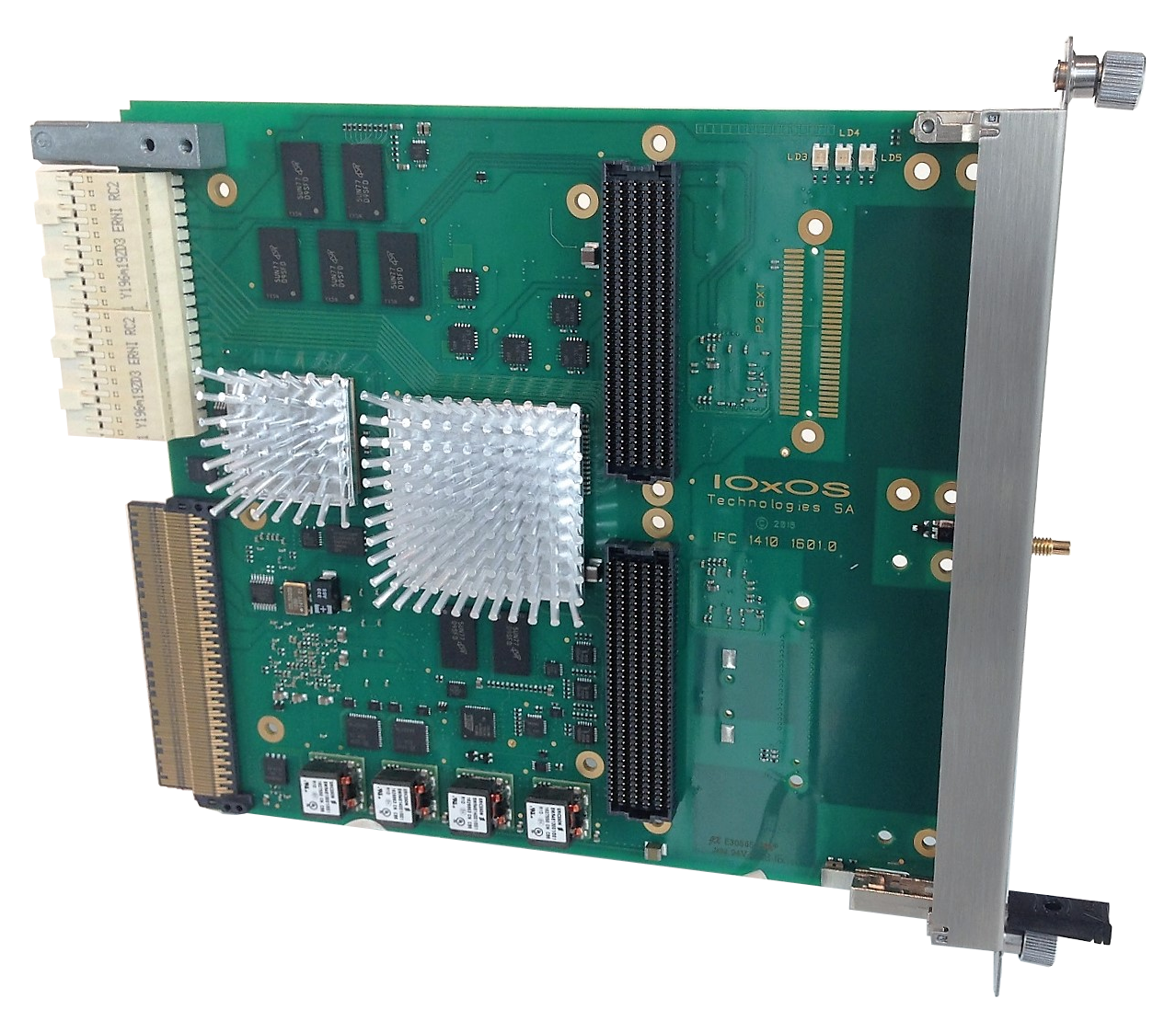

The ADC_3210/3211 is a FMC VITA 57.1-2008 / FMC+VITA 57.4-201 form factor featuring eight (8) ADC channels of 14-bit at 1’300/625 Msps.

The ADC_3210/3211 is based on latest ADC high-speed low-power generation with digital read-out through JESD204B interface, operating from 6.25 Gbps up to 13Gbps.The eight (8) single-ended 50 Ohms analog inputs are supplied through SSMC high frequency connectors. AC coupling (ADC_3210) and DC coupling (ADC_3211) versions are available.

Each ADC channel can optionally be connected to a wide-band digital down-converter (DDC) block, featuring decimation and low-pass / high-pass / band-pass filtering as well as digital I/Q mixing.

Clock tree is implemented with a high precision on-board low jitter low phase noise clock controller LMK04616, fully programmable by the carrier-board. The clock reference source is selectable from front panel SSMC input, FMC/FMC+ clock source or from an on-board ultra-low phase noise VCXO / programmable XCO. The FMC/FMC+ ADC_3210/3211 incorporates precise synchronization mechanism for the dual PLL on-board clock controller LMK04616 and/or ADC devices allowing to keep in phase several units.

A user programmable GPIO SSMB can be defined as user specific TRIGGER, GATE, on-board PLL synchronization for CLOCK replication or any user specific function embedded in the carrier FPGA. A high-speed compactor with programmable level (DAC) is inserted in the GPIO input path.